Context

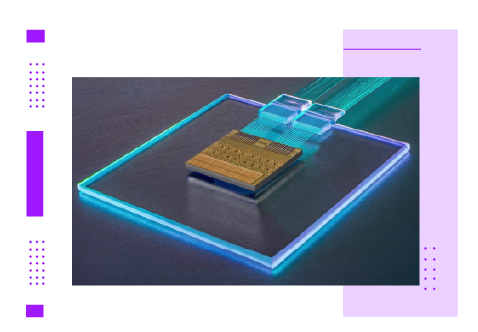

A next-generation SoC program required a multi-chiplet architecture capable of supporting high-bandwidth optical interconnects, low-latency data paths, and AI-driven compute workloads. The system demanded a scalable CPU subsystem, advanced inter-chip communication, and robust debug / security features, all targeting aggressive PPA goals on advanced process technology (TSMC 5nm).

Eximietas led the end-to-end architecture, design, and integration across firmware, RTL, physical design, and silicon bring-up planning. Key responsibilities included:

Concept-to-GDSII Ownership:

Full HW/FW architecture definition and execution across the complete design lifecycle.

Modular Chiplet Architecture:

Enabling seamless integration of multiple IPs and subsystem components across chiplets.

CPU Subsystem Design:

Selection and integration of ARM-based M-series and A-series processors, including boot flow, firmware, and API design.

Network Coverage Layer (NCL):

Low-latency, power-optimized interconnect tailored for efficient chiplet-to-chiplet communication.

System-Level Integration & Bringup:

Ensuring robust interaction across optical interfaces, bus protocols, firmware, and silicon infrastructure.

Concurrent RTL–FW–PD Development:

Ensuring interfaces, timing budgets, and boot flows converged in parallel without impacting schedule.

High-Speed Data Path Validation:

Mixed-signal validation of optical link behavior along with digital protocol correctness.

Aggressive PPA Requirements:

Maintaining optimal performance and area on TSMC 5nm while supporting an expanding IP set.

Emulation for Early Software Enablement:

Aligning firmware, boot chains, and debug logic with pre-silicon prototypes to de-risk first silicon.

Flow Setup for Novel Architecture:

Since the design utilized custom compute IP, Eximietas was responsible for establishing the complete physical design flows and methodologies from scratch. Quality of Results (QoR) Optimization: To ensure timing closure and power efficiency in advanced nodes, the team developed specialized tools and a Python-Based Dashboard. This dashboard provided essential insights for efficient data analysis, facilitating continuous optimization of timing and block-level parameters during Physical Design. High-Density Integration: Successful Physical Design and DFT implementation were achieved for this complex, high-pin-count device, leveraging our experience with large CNICs and complex ASICs.

Eximietas successfully delivered a full GDSII-ready, multi-chiplet architecture with a validated design flow for high-speed optical interconnect applications.

- Delivered fully verified RTL with hierarchical SV-UVM testbenches and AMS mixed-signal simulations.

- Enabled firmware boot readiness through emulation, accelerating system software development.

- Implemented complete DFT strategy enabling efficient ATE coverage.

- Achieved timing closure and PPA targets on TSMC 5nm.

The engagement showcased Eximietas’ capability to execute complex chiplet-based designs, integrating advanced compute, interconnect, and physical design flows with first-silicon success in mind.